## NMOS:

- plus simple à comprendre

- mais pose problème car on est loin des configurations des circuits idéaux

### CMOS:

- Plus complexe

- S'approche des configurations idéales

- Subtilités propres au CMOS pour optimiser des circuits complexes

### Démarche:

- un minimum d'analyse

- principalement axée intuitive, exploitation de la droite de charge

## Puissance dissipée

Caractéristique essentielle en C.I., spécialement en VLSI.

Limite le nombre maximum de portes réalisables sur une puce.

La puissance maximum admissible par chip dépend du type de boîtier.

• De l'ordre de 500 mW à 1 watt.

La puissance dissipée dans un circuit logique a

- une composante statique et

- une composante dynamique.

Puissance statique = puissance dissipée au repos.

• le circuit est alimenté, mais ne change pas d'état.

Puissance dynamique = puissance dissipée pour changer d'état.

Autre caractéristique fondamentale: la puissance dissipée.

Les circuits VLSI se caractérisent par des millions de transistors qui doivent fonctionner en parallèle.

La vitesse à laquelle les portes vont travailler dépendent en partie de l'énergie qui leur est fournie.

On imagine aisément la problématique liée à la puissance maximale que pourrait dissiper le circuit intégré. Au delà de cette puissance, c'est l'intégrité même du circuit qui serait en jeu.

La puissance consommée présente deux caractéristiques:

- une caractéristique dynamique nécessaire uniquement au changement d'état de la porte et donc incontournable.

- Une caractéristique statique qui ne sert à "rien", mais se manifeste à cause de la construction du circuit. Il faut donc minimiser cette caractéristique.

2

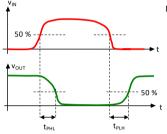

## Exemple de calcul de puissance statique

ne dissipe aucune puissance dans l'état de sortie 1 (transistor bloqué),

- Dissipe une puissance P<sub>stat</sub> = V<sub>cc</sub> I<sub>sat</sub> = V<sub>cc</sub><sup>2</sup>/R avec sortie 0.

- En moyenne: moitié des sorties à l'état 1, et moitié à l'état 0

L'inverseur à transistor bipolaire:

#### Cas de l'inverseur CMOS :

• ne dissipe pratiquement aucune puissance au repos, car un des deux transistors est toujours bloqué.

3

Prenons l'exemple d'un inverseur RTL constitué d'un transistor bipolaire et d'une résistance.

- Lorsque le transistor est bloqué ("0" à l'entrée), aucun courant ne circule, donc aucune consommation n'est détectée.

- Lorsque le transistor est saturé ("1" à l'entrée), un courant circule constamment, alors que le niveau logique est déjà établi ("0" logique à la sortie). Ce courant  $I_{\rm CSAT}$  est inutile mais malheureusement lié à la construction même de l'inverseur. C'est la résistance qui va dissiper cette puissance inutile par effet Joule.  $P_{\rm S} = V_{\rm CC}^2/R$

En moyenne, on a autant de chance d'avoir un "0" et un "1" à la sortie, auquel cas, la puissance moyenne vaut  $V_{CC}^2/2R$

Nous verrons qu'avec la technologie CMOS, cette puissance statique est extrêmement faible.

## Exemple de calcul de puissance dynamique

Lié à la charge ou à la décharge d'une capacité parasite connectée à la sortie de la porte.

La charge s'effectue à travers la résistance de charge R (le transistor est en mode bloqué)

Puissance dynamique dissipée pour une commutation de 0 à 1:

$$E = \int_0^\infty (V_{CC} - V) \cdot i dt = \int_0^\infty (V_{CC} - V) \cdot C \cdot \frac{dV}{dt} dt = \int_{V(0)}^{V(\infty)} (V_{CC} - V) \cdot C \cdot dV$$

$$\text{Avec V}(\infty) = V_{CC} \text{ et V}(0) = 0 \text{ on a } P = \frac{C \cdot V_{CC}^2}{2}$$

Transition inverse: Puissance équivalente dissipée dans transistor.

La puissance dynamique dépend de la fréquence f de commutation

$P_{Dyn} = f.C.V_{CC}^2$

La puissance dynamique intervient pendant le changement d'état de l'inverseur.

Imaginons que la sortie de l'inverseur attaque une charge capacitive. Il faut donc que l'alimentation ( $V_{\rm DD}$ ) fournisse une énergie pour charger la capacité (passage de "0" à "1") et l'alimentation (masse) doit fournir la même quantité d'énergie pour décharger la capacité (passage de "1" à "0").

Le calcul intégral nous donne l'expression de l'énergie nécessaire pour effectuer un cycle complet de charge et de décharge.

Connaissant la fréquence f à laquelle doit travailler le circuit, il est alors possible de connaître le nombre de changements d'états et d'en déduire la puissance dynamique de la porte (par seconde).

## Délai de propagation par porte

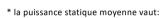

Retard entre transition des signaux de sortie et d'entrée.

Ce retard est lié à divers phénomènes dynamiques, tels que:

- la charge et/ou la décharge de diverses capacités parasites,

- l'évacuation des minoritaires stockés dans la base d'un transistor (bip.) saturé,

Méthode courante pour le délai de propagation:

- Mesurer le délai entre les points à "50%" des signaux d'entrée et de sortie.

- Délais de propagation différents pour montée et descente,

Temps de propagation = moyenne entre ces deux temps

$$t_{PD} = \frac{1}{2}(t_{PHL} + t_{PLH})$$

Pour qu'il y ait basculement, il est intuitif de considérer que la sortie d'une porte logique peut généralement être interprétée lorsque un seuil correspondant à la moitié de la tension  $V_{DD}$  a été atteint (en montant ou en descendant).

Ce seuil est arbitraire mais représente une valeur objective pour notre évaluation.

Il est alors possible de fixer les temps de retard pour les basculements dans le sens montant ou descendant.

t<sub>PHL</sub> correspond au basculement de la sortie du niveau "1" vers le niveau "0" (lorsque l'entrée est évidemment passée du niveau "0" au niveau "1"). C'est l'écart entre le moment où l'entrée atteint 50% de la charge et le moment où la sortie atteint 50% de la décharge.

Réciproquement, t<sub>PLH</sub> correspond au basculement de la sortie du niveau "0" vers le niveau "1" (lorsque l'entrée est évidemment passée du niveau "1" au niveau "0"). C'est l'écart entre le moment où l'entrée atteint 50% de la décharge et le moment où la sortie atteint 50% de la charge.

## La logique NMOS

### Technologie adaptée à la réalisation de circuits logiques VLSI:

- 1- Structure très simple (techno simplifiée conception simplifiée)

- ex: Pas d'isolation nécessaire entre transistors voisins (diodes en inverse)

#### conséquence: économiquement moins cher

- 2- Surface de silicium réduite. conséquence:

- Plus économique que le bipolaire

- Plus de puissance de calcul pour surface identique

mais présence d'une résistance gourmande en surface

3- Impédance d'entrée quasi infinie (voir cours sur les A.O.)

Utilisation de N-MOS plutôt que des P-MOS car:

$\mu_n > \mu_p \longrightarrow logique N-MOS plus rapide que P-MOS$

Inverseur à charge résistive

6

## Ensemble de caractéristiques qui contribuent à:

- diminuer les coûts de la technologie ou de la conception

- et/ou d'augmenter la puissance de calcul

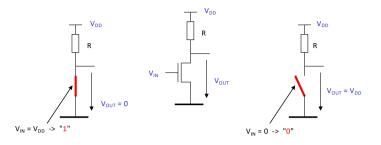

# Comportement idéal = interrupteur

Avec une charge reliée à V<sub>CC</sub>, on réalise une logique de type NOT

Si le MOS se comporte comme un interrupteur on obtiendrait bien:

1) des niveaux logiques idéaux

2) des temps de commutation optimaux, car les transistors n'interviendraient plus en termes résistifs (ils correspondraient à des circuits fermés R= infini ou fermés: R=0) ou capacitifs.

Seul l'environnement imposerait le calcul

## Comportement idéal = interrupteur

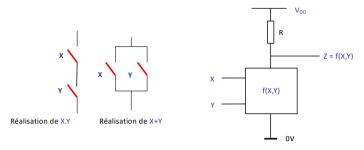

Réalisation de fonctions avec des interrupteurs

La nature des fonctions dépend de la structure série ou parallèle des composants

Quelles sont les configurations possibles pour de tels montages:

- 1) Si un chemin conduit le courant, alors on obtient 0V ("0") à la sortie. La chute de potentiel est absorbée par la résistance R.

- 2) Si aucun chemin ne conduisait le courant, alors on obtient  $V_{DD}$  ("1") à la sortie. Pas de chute de potentielle sur la résistance R, car pas de courant.

Quels sont les chemins que peut emprunter le courant:

- 1) dans une configuration X.Y, le courant circule si X ET Y sont fermés

- 2) dans une configuration X + Y, le courant circule si X OU Y sont fermés

Par analogie avec la mécanique on dira que:

X fermé est assimilé à "on appuie sur l'interrupteur" ou "1" à l'entrée

X ouvert est assimilé à "on relâche l'interrupteur" ou "0" à l'entrée

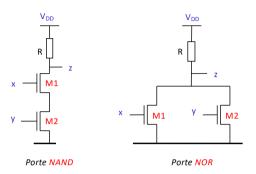

# Circuits logiques N-MOS:

Exemples de réalisations:

"on appuie sur l'interrupteur" est remplacé par  $V_{\text{DD}}$

"on relâche l'interrupteur" est remplacé par 0V

Malheureusement, M1 et M2 ne sont pas de vrais court-circuits Cependant ce sont de bons circuits ouverts

## Conséquence:

- Z="0" laisse à désirer

- Z = "1" OK!

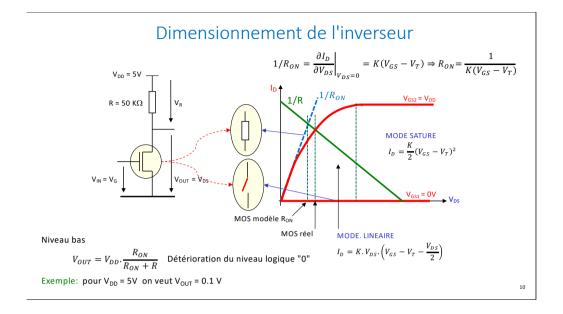

Mise en évidence du mauvais "0", illustré avec l'inverseur.

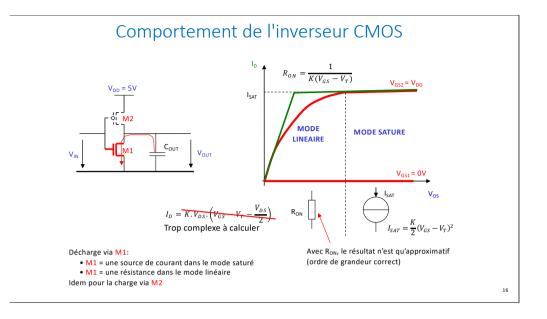

Le MOS se comporte comme une résistance lorsque V<sub>DS</sub> tend vers 0V.

Dans ce cas, inutile d'espérer 0V à la sortie.

L'expression du  $R_{ON}$  est obtenue lorsque le transistor est dans le mode linéaire ( $V_{DS} \le V_{GS}$  -  $V_T$ ). Cette expression d'une pente est calculée à partir de la dérivée de  $I_D$  par rapport à  $V_{DS}$  (lorsque  $V_{DS} = 0$ )

On a donc un diviseur résistif qui altère d'autant plus  $V_{\text{OUT}}$  que  $R_{\text{ON}}$  est grand (ou R petit).

Or  $R_{\rm ON}$  dépend des dimensions du transistor quant à R, l'intégration suggère une limitation de sa taille.

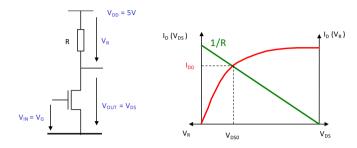

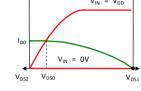

# Vision graphique: Exploitation de la droite de charge

Inconvénient majeur : Détérioration du niveau logique "0"

11

Lorsque le transistor conduit, le courant le traversant et celui de la résistance sont identiques (chemin unique de  $V_{DD}$  à la masse).

L'intersection des deux courbes donne un point unique  $(V_{DS0},\,I_{D0})$  où  $V_{DS0}$  correspond à la tension à la sortie de l'inverseur.

On constate que cette tension peut être significativement éloignée de 0V.

On "améliore" cette tension de deux manières.

- 1) Graphiquement, on voit que  $V_{\rm DS0}$  diminuerait si la droite de charge s'affaissait. Cela implique que R doit augmenter.

- 2)  $V_{DS0}$  diminuerait aussi, si la pente au démarrage de la courbe (1/ $R_{ON}$ ) augmentait, ce qui signifie que  $R_{ON}$  diminue, ou encore que la conductivité du MOS dépendant de  $K=\mu C_{OX}W/L$  augmente.

Or µ dépend de la nature et de la technologie

Cox dépend de la nature et de la technologie

En revanche W/L dépend de la conception et pourrait augmenter à "volonté", ce qui donnerait simplement un transistor plus grand.

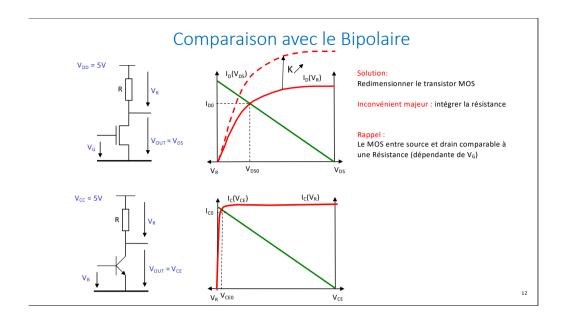

Les deux caractéristiques se ressemblent.

Pour le bipolaire, à ce stade des connaissances du cours, il semble que seule R pourrait être modifiée pour améliorer  $V_{\text{CE0}}$  qui est naturellement plus bas que  $V_{\text{DS0}}$ .

Par contre V<sub>DS0</sub> est améliorée grâce au dimensionnement du MOS.

Dans les deux cas, il y a un problème majeur: L'intégration de R.

$I_D(V_{DS2})$

Si les deux transistors ont une conductivité identique Dégradation du "0" logique

Si M1 a une meilleure conductivité

Dégradation du "0" logique minimisée

$I_D(V_{DS1})$

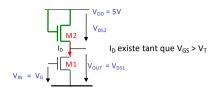

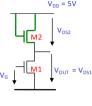

1) Première solution: remplacer R par un transistor M2 qui devrait conduire tout le temps (comme R). La droite de charge de la résistance est remplacée par la caractéristique  $I_D = f(V_{DS2})$  de M2.

#### Attention:

- $I_{D2}=I_{DMAX},$  lorsque toute la tension  $V_{DS2}=V_{DD}$  . Dans le même temps, il reste  $V_{DS1}=0V$  aux bornes de M1.

- $I_{D2}$  =  $I_{DMIN}$  = 0, lorsque toute la tension  $V_{DS1}\,$  =  $V_{DD}$  . Il ne reste plus rien aux bornes de M2,  $V_{DS2}$  = 0V.

La droite de charge est donc remplacée par une caractéristique du MOS "mirorisée".

- Si M1 et M2 sont de mêmes tailles, alors les deux caractéristiques sont identiques (disons similaires). L'analyse graphique met aussi en évidence un courant unique, correspondant à l'intersection des deux caractéristiques. La tension  $V_{DS0}$  vaut quasiment  $V_{DD}/2$ , ce qui est épouvantable pour un "0".

- 2) Pour améliorer cette situation, il est possible d'affaisser la caractéristique de M2. Ceci est possible si la pente à l'origine de M2 s'écroule. Il faut pour cela que K2 (conductivité de M2) soit plus petite. Diminuer K2 suppose que W/L diminue, ou encore que L augmente.

13

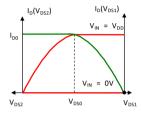

3) Reste un problème non mis en évidence avec R, la dégradation du "1".

## Améliorations possibles

Dégradation du "1" logique  $V_{OUT} \le V_{DD} - V_{T}$

Deux alimentations

Transistor déplété avec V<sub>⊤</sub> < 0

14

Le "1" se dégrade, car la tension  $V_{OUT}$  ne peut pas être supérieure à  $V_{DD}$  -  $V_{T}$ .

En effet, le transistor conduit si  $V_{GS} > V_T$ , or:

$$V_G = V_{DD}$$

et  $V_S = V_{OUT} \Longrightarrow V_{DD}$  -  $V_T \gt V_{OUT}$

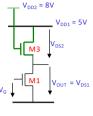

### Solution 1:

Connecter  $V_{G2}$  à une tension  $V_{DD2}$  telle que  $V_{OUTMAX} = V_{DD2}$  -  $V_T > V_{DD}$

Ceci est possible par exemple avec une tension  $V_{DD2} = 8 \text{ V}$

Si  $V_T = 1$  V, on pourrait monter  $V_{OUT}$  jusqu'à 7V, donc largement suffisant pour atteindre les 5V.

Inconvénient majeur: Deux alimentations.

### Solution 2:

Est-ce qu'il existe des transistors où  $V_T \le 0V$

OUI!!! Les transistors déplétés.

Dans le troisième montage, V<sub>OUT</sub> peut monter jusqu'à V<sub>DD</sub> car

$$V_{GS} = 0V > V_{T}.$$

Attention aux dimensions de M1 et M4 (voir transparent précédent)

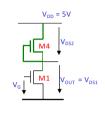

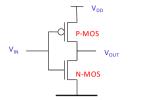

# Principe de l'inverseur CMOS

Remplace quasi toutes les autres technologies. Caractéristiques proches de la famille logique idéale :

- Excellent comportement pour des charges capacitives

- Consommation quasi nulle au repos (tant dans l'état 0 que dans l'état 1 de la sortie)

- Une seule tension d'alimentation V<sub>DD</sub>

- Niveaux logiques = Niveaux de l'alimentation (0 & V<sub>DD</sub>)

- La sortie change d'état pour V<sub>in</sub> ~ V<sub>DD</sub>/2

- · Grande marge de bruit

- Vitesse élevée

15

Pour obtenir des caractéristiques symétriques (par exemple  $t_R = t_F$ ; temps de montée = temps de descente), il faut que les deux transistors aient un comportement identique. En terme de conductivité cela signifie que  $K_N = K_P$ .

Or  $\mu_N \sim 2~\mu_P$ , si  $C_{OX}$  est le même =>(W/L)\_P = 2(W/L)\_N. Le transistor P est généralement 2 fois plus gros que le N.

La décharge du condensateur via M1 s'effectue en deux phases.

$\Phi 1 \colon \text{temps pour passer de } V_{\text{DD}} \, \grave{a} \, V_{\text{DSAT}}.$

Le MOS se comporte comme une source de courant.

$\Phi 2$ : temps pour passer de  $V_{DSAT}$  à 0V.

Le MOS est approximé par une résistance.

L'analyse de la charge du condensateur via M2 s'effectue selon les mêmes principes.

De plus, si les deux transistors ont des conductivités identiques,  $K_{\rm N}$  =  $K_{\rm P}$ , alors les temps de charge et de décharge sont identiques.

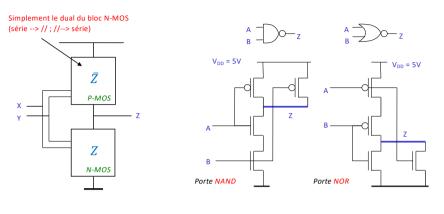

# Réalisation d'une porte logique en CMOS

Comme dans l'inverseur, on veut générer des fonctions booléennes complexes, garantissant la dualité des zones N et P.

Si la zone P conduit, la zone N est bloquée et réciproquement.

Imaginons une NOR à deux entrées. La zone N conduit si au moins l'un des transistors conduit. Dans ce cas la zone P est bloquée si au moins l'un des transistors P est bloqué.

La zone N est bloquée si les deux transistors sont bloqués. Dans ce cas la zone P conduit si les deux transistors P conduisent.

On voit bien que la zone N doit être structurée avec des éléments en parallèle, alors que la zone P est configurée en série.

Imaginons une NAND à deux entrées. La zone N conduit si les deux transistors conduisent. Dans ce cas la zone P est bloquée si les deux transistors P sont bloqués.

La zone N est bloquée si au moins l'un des transistors est bloqué, alors que la zone P conduit si au moins l'un des transistors conduit.

On voit bien que la zone N ne peut être configurée qu'en série, alors que la zone P doit l'être en parallèle.

La dualité entre les zones N et P se manifeste en termes de sérialité et de

17

parallélisme des structures.

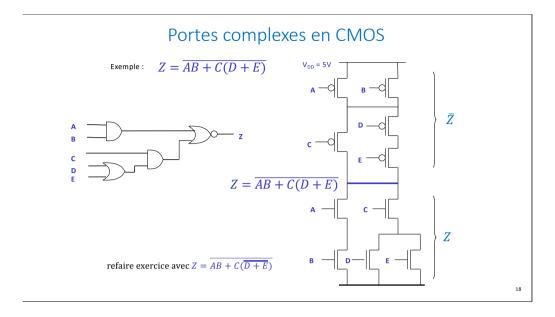

Ce type de fonction (fonction booléenne en inverse) peut être réalisée avec une seule porte complexe.

Les produits sont réalisés avec des transistors séries.

Les sommes sont réalisées avec des transistors parallèles.

L'opération de plus haut niveau "." ou "+" donnera la nature de la porte (NAND ou NOR).

Dans l'exemple ci-dessus, il s'agit d'une NOR, intégrant des éléments séries A.B et série - parallèle C.(D+E)

Comme avant, le dessin de la zone N nous donne directement, par dualité structurelle, le dessin de la zone P.